完全自分用のページですので、質問とか来ても答えれないです

環境

FPGA ALINX_AX7103

vivado 2024.1

コード

サンプルコード文字化けしててよくわからなかったから下に日本語にしたやつ投下

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// module_name: pll_test

//////////////////////////////////////////////////////////////////////////////////

module pll_test(

input sys_clk_p, // システムクロックの正入力

input sys_clk_n, // システムクロックの負入力

input rst_n, // リセット信号(負論理)

output clk_out // PLLクロック出力 J5_Pin3

);

///////////////////// 差動信号を単一信号に変換 ////////////////////////////

wire sys_clk_ibufg; // バッファを介したシステムクロック信号

IBUFGDS #

(

.DIFF_TERM ("TRUE"), // 差動終端を有効にする

.IBUF_LOW_PWR ("FALSE") // 低消費電力モードを無効にする

)

u_ibufg_sys_clk

(

.I (sys_clk_p), // 差動入力(正)

.IB (sys_clk_n), // 差動入力(負)

.O (sys_clk_ibufg) // 出力(単一信号)

);

wire locked; // PLLロック状態信号

wire pll_clk_o; // PLLクロック出力信号

///////////////////// PLL IP 設定 ////////////////////////////

clk_wiz_0 clk_wiz_0_inst

(// クロック入力ポート

.clk_in1(sys_clk_ibufg), // 入力 200MHz

// クロック出力ポート

.clk_out1(), // 出力 200MHz

.clk_out2(), // 出力 100MHz

.clk_out3(), // 出力 50MHz

.clk_out4(pll_clk_o), // 出力 25MHz

// 状態および制御信号

.reset(~rst_n), // 入力(リセット信号、負論理を反転)

.locked(locked)); // 出力(ロック状態)

/////////////// ODDR2を使用してクロック信号を汎用IOに出力 //////////////////

ODDR2 #(

.DDR_ALIGNMENT("NONE"), // 出力アライメントを「なし」に設定

.INIT(1'b0), // Q出力の初期状態を0に設定

.SRTYPE("SYNC") // セット/リセットのタイプを「同期」に指定

) ODDR2_inst (

.Q(clk_out), // 1ビットのDDR出力データ

.C0(pll_clk_o), // 1ビットのクロック入力(正)

.C1(~pll_clk_o), // 1ビットのクロック入力(負)

.CE(1'b1), // 1ビットのクロック有効入力(常に有効)

.D0(1'b1), // 1ビットのデータ入力(C0に関連)

.D1(1'b0), // 1ビットのデータ入力(C1に関連)

.R(1'b0), // 1ビットのリセット入力(リセットなし)

.S(1'b0) // 1ビットのセット入力(セットなし)

);

endmodule XDC

############## clock define##################

set_property PACKAGE_PIN R4 [get_ports sys_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports sys_clk_p]

set_property PACKAGE_PIN T4 [get_ports sys_clk_n]

set_property IOSTANDARD DIFF_SSTL15 [get_ports sys_clk_n]

############## reset_n key define##################

set_property PACKAGE_PIN T6 [get_ports rst_n]

set_property IOSTANDARD LVCMOS15 [get_ports rst_n]

############## pll output define##################

set_property IOSTANDARD LVCMOS33 [get_ports clk_out]

set_property PACKAGE_PIN W16 [get_ports clk_out]XDCはボードによって変わるから、もしこの情報を使うならちゃんとデータシート見て設定してください

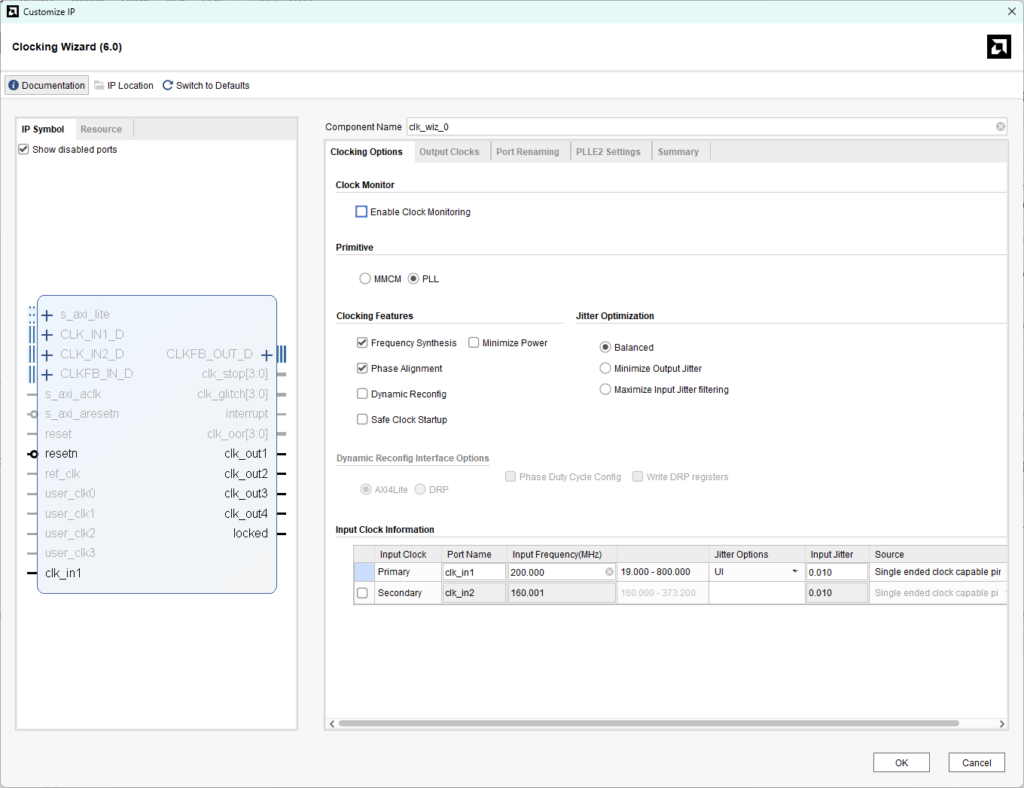

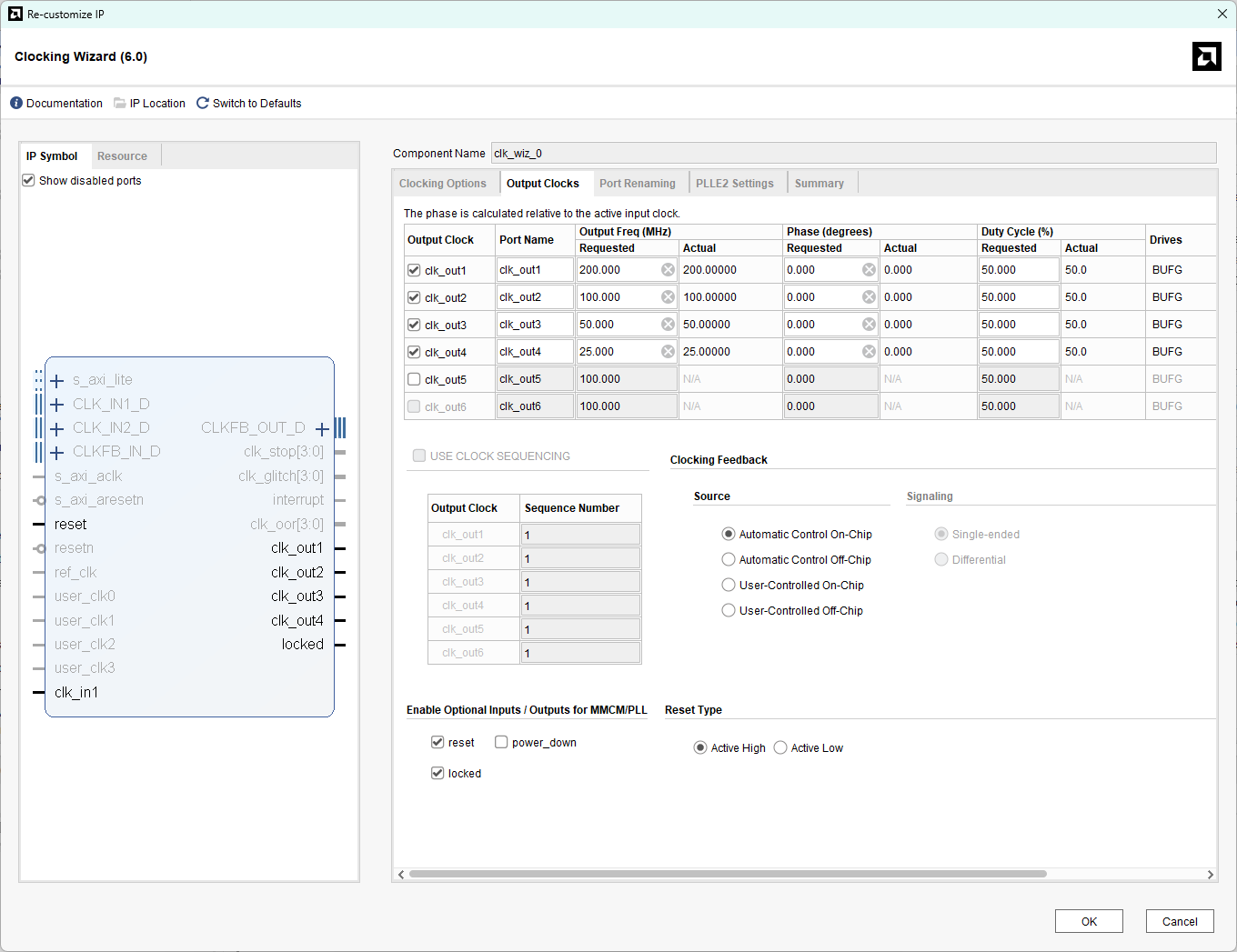

IP

左のサイドバーより、 IP Catalog > Search: Clocking Wizard

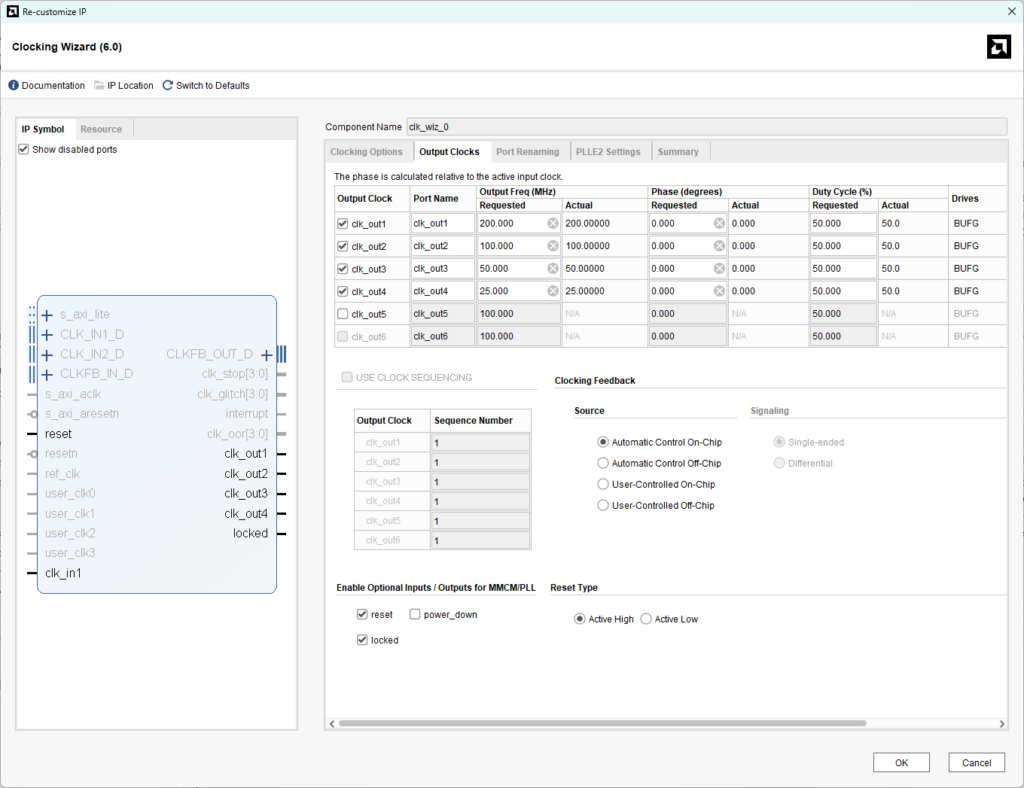

設定 今回は入力が200MHz 出力は200MHz, 100MHz, 50MHz, 25MHz

出力させた

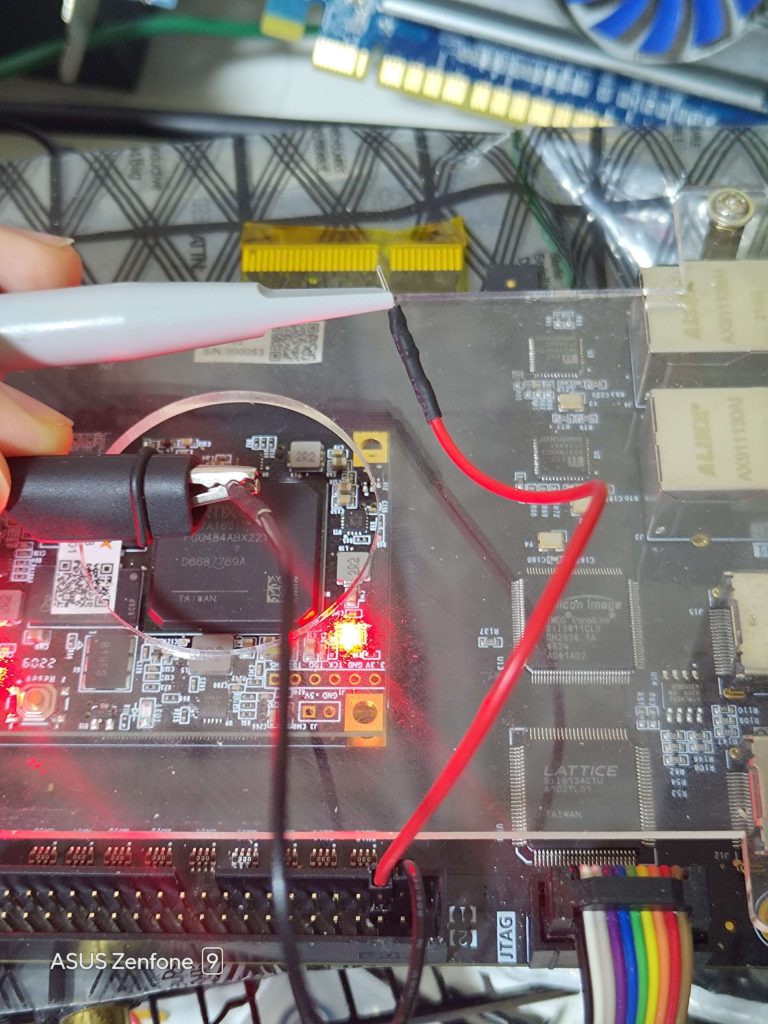

FPGAさんのIOから出力させてみる。こいつがどこまで行けるか知りたいよね、

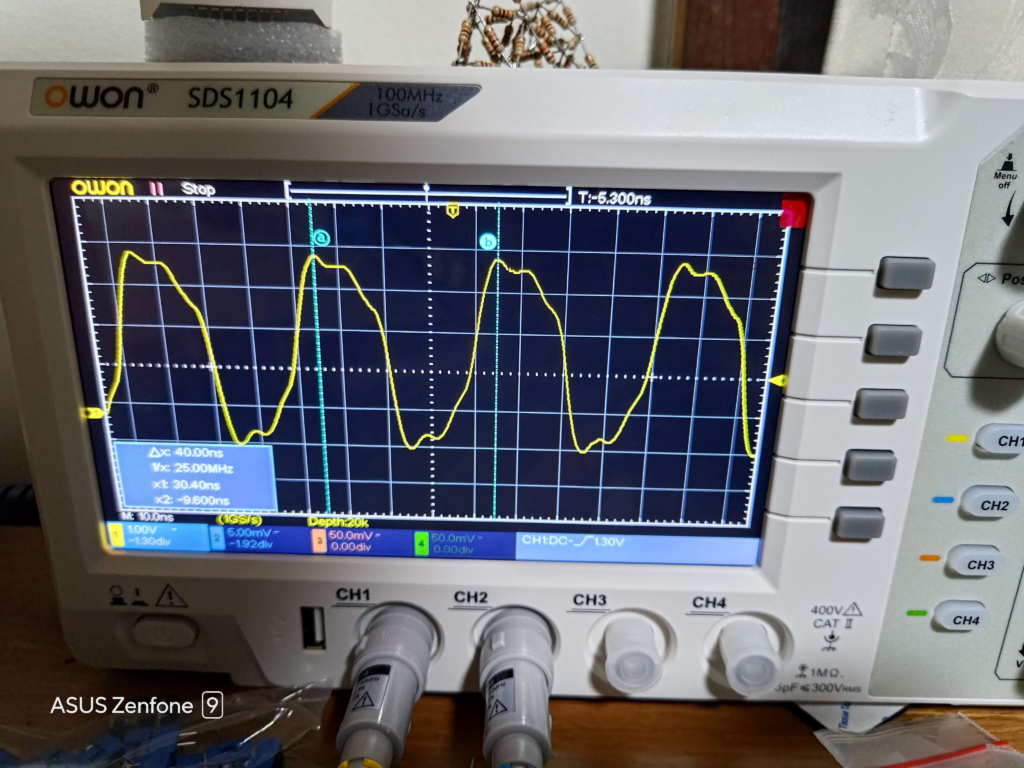

25MHz

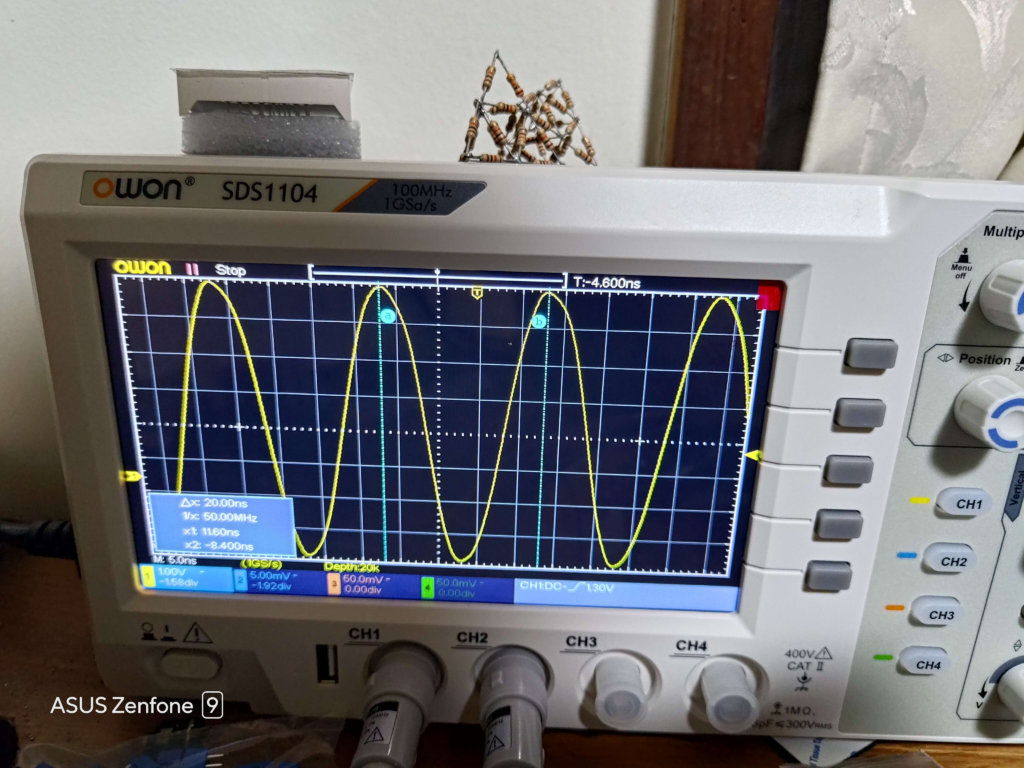

とりあえずこのプログラムで一番遅い25MHz なんか波形が揺れてるけどとりあえず動いてそう

ちゃんと25.00Mhzで動作してる

1.3Vぐらいで出力されている。

50Mhz

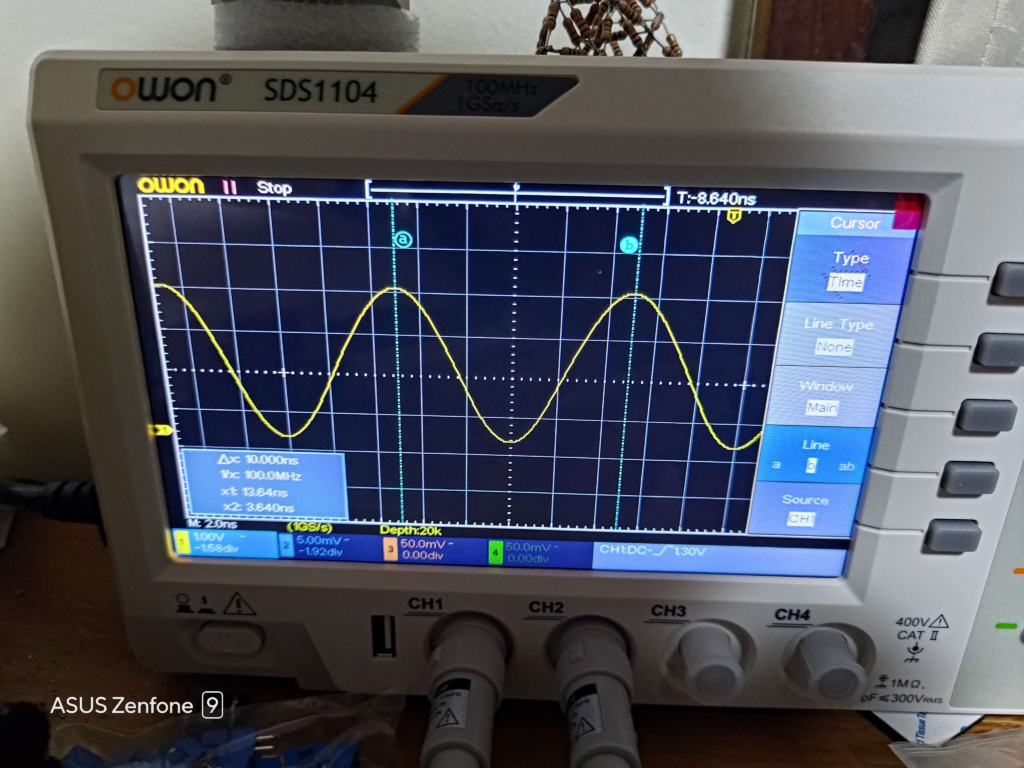

めちゃんこ波形がきれいになった そしてちゃんと50.00MHz

100Mhz

200MHz

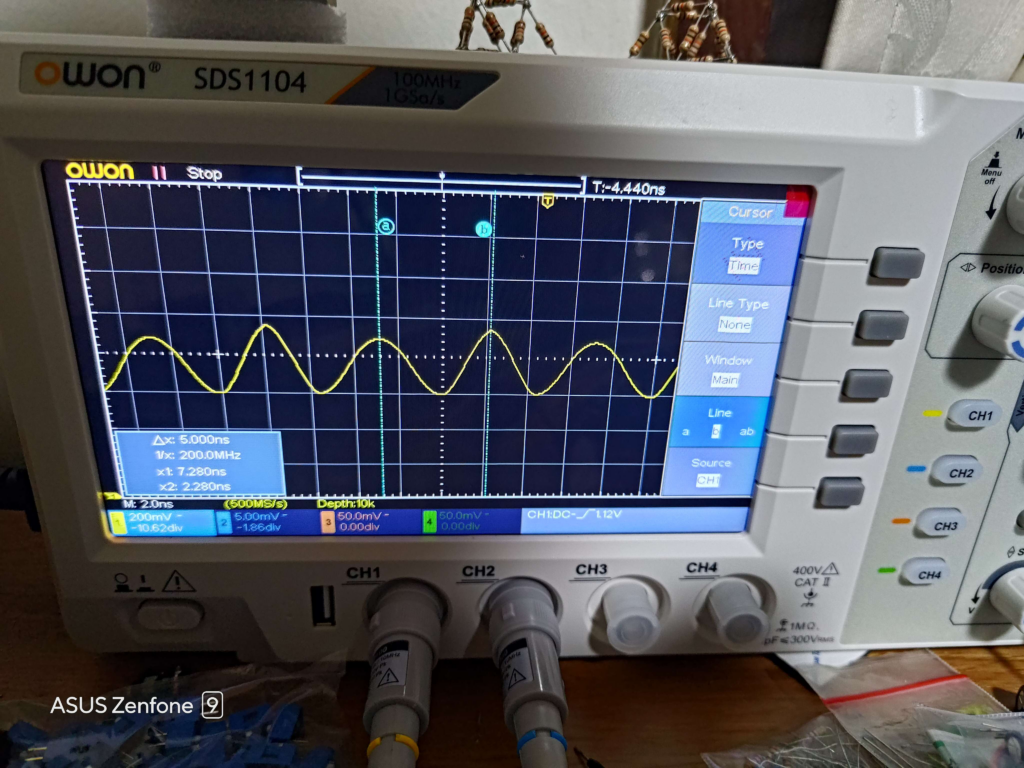

最高速で出力させた 電圧が低いのと、波形が奇数偶数で形が変わってるけど、それでも200.0MHzが出力されてる

、、

クロックジェネレータとして使おうかな(

メモ

wire sys_clk_ibufg; // バッファを介したシステムクロック信号

IBUFGDS #

(

.DIFF_TERM ("TRUE"), // 差動終端を有効にする

.IBUF_LOW_PWR ("FALSE") // 低消費電力モードを無効にする

)

u_ibufg_sys_clk

(

.I (sys_clk_p), // 差動入力(正)

.IB (sys_clk_n), // 差動入力(負)

.O (sys_clk_ibufg) // 出力(単一信号)

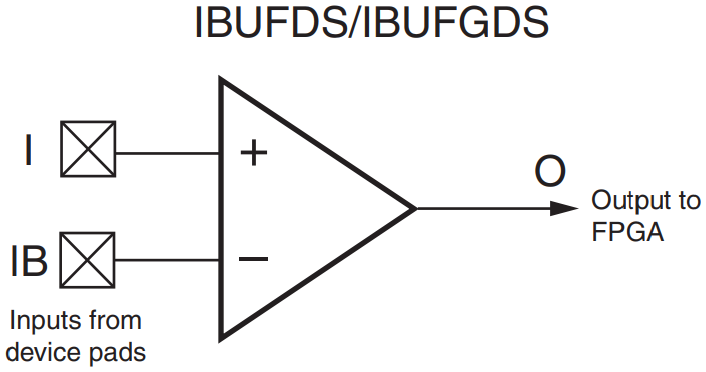

);差動ペアのsys_clk_pとsys_clk_nを受け取り、sys_clk_ibufgに変換している部分IBUFGDSはxilinxのFPGAで使う差動入力バッファってものらしい 差動ペアを処理するためのバッファさん

Grok君に聞くと、

- IBUF: Input Buffer(入力バッファ)の略。

- G: Global(グローバルクロック用)を意味する。

- DS: Differential Signaling(差動信号)を扱うことを示す。

つまり、IBUFGDS は「差動信号を受け取ってグローバルクロックバッファに変換する入力バッファ」という意味です。FPGA内部のクロック配線網に信号を供給するのに適しています。

らしい、合ってるかは知らんけど、

これまたGrokの情報だけど、

.DIFF_TERM (“TRUE”)

差動終端(Differential Termination)を有効にします。外部から来た差動信号の終端抵抗をFPGA内部で処理する設定で、信号の反射やノイズを減らす効果があります。

.IBUF_LOW_PWR (“FALSE”):

低消費電力モードを無効にします。低消費電力にすると信号の品質が落ちる可能性があるため、ここでは性能優先で「FALSE」に設定されています。

らしい、まぁ、LLMを信用するかしないかはあなた次第 おまじないみたいな感覚でいいか、動いてるんだし

コメント